Among the many benefits of photonics is the ability to leverage the properties of light to enable high-speed and low-loss communication in optical data communication, biomedical applications, automotive technology, and artificial intelligence domains.

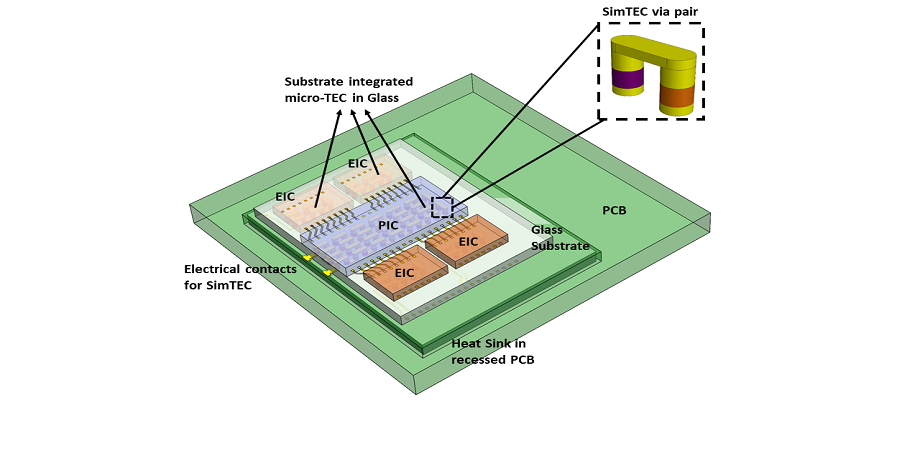

Diagram showing the SimTEC architecture in glass substrate with SimTEC vias operating in the central region of the electronic chips (EIC) and photonic chip (PIC) with the chip’s peripheral I/Os dedicated for electrical connection in the photonic package. Image Credit: The Authors, doi: 10.1117/1.JOM.4.1.011006.

Diagram showing the SimTEC architecture in glass substrate with SimTEC vias operating in the central region of the electronic chips (EIC) and photonic chip (PIC) with the chip’s peripheral I/Os dedicated for electrical connection in the photonic package. Image Credit: The Authors, doi: 10.1117/1.JOM.4.1.011006.

Complex photonic circuits made up of various integrated photonic elements on a photonic chip are used to achieve these benefits. The photonic chips are then supplemented with electronic chips to perform specific tasks like modulation, amplification, and light source operation. One essential component of photonic packaging is the close integration of electronic and photonic chips on a substrate.

In the electrical, optical, mechanical, and thermal domains, photonic packaging is essential to the efficient operation of electronic and photonic chips. Effective thermal control becomes essential in small packages, where variations in ambient temperature and thermal interference between electronic and photonic chips can cause photonic chips to perform poorly.

Glass substrates are important in this case because the substrate provide benefits like a small form factor, minimal electrical loss, and a platform that can be manufactured at the panel level. The substrates have been extensively explored as a co-packaging platform for electronic and photonic chips. Glass substrates also spread heat less laterally between electronic and photonic chips due to their low thermal conductivity.

Through-glass vias (TGVs) are incorporated into glass substrates to enable efficient heat dissipation from electronic chips. Adding micro-thermoelectric coolers (micro-TECs) to a chip’s underside to provide active temperature control is another thermal management technique.

In research published in the Journal of Optical Microsystems, a combination of TGVs and micro-TEC technologies termed “substrate integrated micro-thermoelectric coolers (SimTEC)” were introduced.

To guarantee the thermal stability of the photonic and electronic chips within the package, SimTEC uses TGVs that are partially filled with copper and thermoelectric materials. This new method enhances system-level cooling strategies. Parnika Gupta and associates from University College Cork, Ireland, investigated how glass substrates affected segmented via thermal performance and contrasted it with free-standing micro-TEC pillars.

The scientists examined how SimTEC’s cooling performance was affected by diameter, height, pitch, and fill-factor. Specifically, when chips are flip-chip bonded on the glass substrate, the technology lowers thermal resistance between the TEC surface and the chip interface and offers precise thermal control within the package.

A temperature stabilization range of 18.6 K or a maximum cooling of 9.3 K is indicated by simulations using design of experiments (DOE). Additionally, compared to the cooling performance variation of the free-standing micro-TEC unicouple, the study highlighted a six-fold greater variation in cooling performance with the variation in via geometry. Future SimTEC-integrated architectures may perform better if the properties of thermoelectric materials are optimized.

Journal Reference:

Gupta, P., et al. (2024) Substrate integrated micro-thermoelectric coolers in glass substrate for next-generation photonic packages. Journal of Optical Microsystems. doi.org/10.1117/1.JOM.4.1.011006